Abstract

We present our recent developments on silicon technologies dedicated to the packaging of nano-objects/nano-devices. These technologies aim at both protecting and electrically connecting a nanoscale device positioned on a perfect Si(001)-(2 × 1):H surface smoothed thanks to a 950 °C thermal treatment. The nano-device is connected to nanopads implanted on the silicon surface. Each nanopad is linked to a nanovia which is locally achieved by etching and filling processes operated in a FIB (Focused Ion Beam) equipment. Impacts of the FIB process on via morphology and properties are depicted. Nanopads are fabricated through the local implantation of arsenic, and the effect of the surface smoothing thermal treatment on the dopants diffusion length is estimated by simulation and then experimentally explored. Key process steps such as the etching of a deep cavity and the surface protection with a temporary cap are also described, and a first assembly consisting in a substrate equipped with nanopads and directly bonded with a cap substrate is presented.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

1 Introduction

During the last past years, a new research field named “3D integration” has been introduced in microelectronics [1, 2]. This new field aims at increasing the density of functionalities while taking advantage from the interconnection length decrease, leading to both energy consumption and signal delay decreases. The main key process that has put forward this technology concerns the “Through Silicon Via (TSV)” development. TSV permits the electrical connection of different components in the third dimension [3, 4]. The devices of the stack are connected together thanks to copper pillars, themselves connected to TSV. Consequently and in order to address higher density of interconnects, this technology now follows a roadmap which consists in increasing the aspect ratio of the TSV. One example for solving this problem is the use of carbon nanotubes (CNT) as TSV [5–10]. They present a higher aspect ratio and a higher conductivity than the copper TSV. This kind of solution is part of a field that could be named “nanomaterials for packaging” which is related to a global “nanopackaging” field [11, 12]. It aims at improving packaging solutions thanks to novel materials as those belonging to the class of nanomaterials. Among them, nanoparticles are also imagined as potential solutions for packaging; the main property that is used in this case is the possibility to achieve an assembly between two parts by a nanoparticle sintering process at a temperature lower than 300 °C. A so-called sintering silver-based Low-Temperature Joining Technology (LTJT) has been developed for die attachment [13–18] or wafer-level bonding [19].

Besides these packaging technologies, a need now appears on the nano-object packaging. One solution, which is today explored in the research laboratories for the fabrication of atomic-scale devices, relies upon the use of the tip of a Scanning Tunneling Microscope (STM) [20]. However, this solution is not suitable for a large production of devices, and technologists are facing a new challenge where the main difficulty is to connect very small objects to electrical connectors, or pads, which means going from the device’s scale (atomic or nanometric) to the chip’s scale (micrometric). In particular, the separating distance between pads is requested to be as small as the size of the object to be connected. This challenge opens a research field that could be named “packaging for nano-devices,” which can take benefit from the solutions developed both in the classical packaging field and the 3D integration field. Some nano-devices, such as atomic wires for instance, indeed require a specific receiving surface (addressed by the packaging field through the development of surface treatments), which implies vertical electrical connections to avoid its damaging (connections addressed by the 3D integration field through the development of vias or TSV). One of the main challenges is then to achieve the fabrication of two nanoscale vias (later referred to as nanovias) separated by the smallest possible distance, meaning in the order of magnitude of a few tens of nanometers. The nano-object is connected to nanovias thanks to nanopads which are processed on the receiving surface. A technology based upon the nanovias implementation with a Focused Ion Beam (FIB) has already been explored [21, 22]. The step beyond such a technology is to develop a compatible capping to protect the nano-device; this is under development at CEA-LETI, and the first results will be presented in this paper.

First, the technological process flow necessary to develop this kind of chip will be described. The FIB-based processes required for the nanovia fabrication will be presented, and their influence on nanovia morphology will be detailed. Then, nanopads process will be investigated both by simulation and experiment. Lastly, the first integration of a reconstructed substrate equipped with nanopads and protected with a cap substrate will be presented.

2 Specifications for Atomic-Scale Device Packaging

The problem to solve will be clearly understood by referring to Fig. 1.

Drawing of a chip connecting a molecule, a nano-object, or an atomic-scale circuit. The electrical interconnection comprises (i) nanopads to which the molecule is connected, (ii) nanovias achieved with a FIB tool through a membrane delimiting one wall of the cavity, and (iii) backside lines and contacts. Gray and green parts correspond to silicon, whereas the blue part is silicon oxide

This figure describes a die comprising an atomic-scale device, such as a molecule, on the front side of a Silicon-On-Insulator substrate (SOI), and protected with a hermetically bonded silicon cap. This cap is equipped with a cavity (corresponding to the atomic-scale device) and lateral bevels to facilitate its release. The atomic-scale device is connected to nanopads consisting in implanted areas in the silicon layer of the SOI substrate. These ones are linked to nanovias etched through a membrane previously prepared on the backside of the SOI substrate.

The fabrication of the atomic-scale device needs a perfectly ordered surface to avoid any variability. Perfect surface size specification is about 100 × 100 nm2 which requests the surface to present terraces with a similar size. The surface is thus reorganized according to a Si(001)-(2 × 1):H structure [23] obtained with a smoothing treatment carried out under hydrogen at high temperature (between 950 and 1100 °C) [24]. Such H-passivated surface is not very stable at ambient atmosphere and consequently requires a temporary protection. It has been achieved through the addition of a temporary cap substrate. The debonding ability of this cap is ensured by a low-energy direct hydrophobic bonding process. This protection step however severely limits further thermal treatments, as the bonding energy is strongly reinforced with temperature. Surface smoothing and protection are consequently performed at the end of the integration process. The corresponding process flow is presented on Fig. 2.

This flow includes 11 technological steps:

-

Step 1: Fabrication of localization marks in order to be able to identify the area of interest and to localize the nanopads during the nano-object positioning (where the atomic-scale device is achieved).

-

Step 2: Encapsulation of the substrate with a SiO2/Si3N4/SiO2 tri-layer mask in order to protect the wafer during the backside cavity deep etching.

-

Steps 3 and 4: Hard mask patterning for cavity etching.

-

Step 5: Cavity wet etching (until the buried oxide layer (BOX)).

-

Step 6 and 7: Cavity walls oxidation and front side SiO2 etching.

-

Step 8: Nanovias etching in a FIB tool and dopant implantation through the nanovias (nanopads fabrication).

-

Step 9: Encapsulation layers removal.

-

Step 10: Surface reconstruction and bonding of a temporary protection. In the meantime, doping species are activated.

-

Step 11: Nanovias filling and backside interconnections achievement.

According to this flow, one can distinguish four major and challenging modules which are steps 5, 8, 10, and 11. Once this die has been obtained, three main additional steps need to be validated and concern the cap release, the atomic-scale device construction, and the final hermetic capping at a temperature that does not damage the device. This paper will focus on the major modules 5, 8, and 11, related to the fabrication of the nano–micro connecting path (nanopads, nanovias, and the backside interconnection, at the bottom of the backside cavity). The surface module (step 10) has already been investigated, and the published results will be reminded at the beginning of the next chapter.

3 Technological Steps

3.1 Surface Smoothing and Temporary Protection

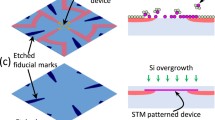

Silicon surface smoothing is a prerequisite for STM-based atomic-scale device design as a perfectly ordered surface is needed. This process is carried out at wafer scale in a Reduced Pressure–Chemical Vapor Deposition (RP-CVD) reactor at high temperature (950–1100 °C) and leads to a perfectly ordered hydrophobic Si(001)-(2 × 1):H surface [25]. This H-passivated surface is not stable and needs to be protected with a removable cap. Among the possible bonding solutions [24], silicon direct bonding appears as the most relevant option:(i) The bonding process can take advantage of hydrophobic smoothed surface. (ii) Such a bonding is characterized by a low-energy interface, which is strengthened with a temperature as high as 400 °C, below this temperature, the substrates can be debonded, which makes this bonding process compatible with a temporary capping [26]. (iii) Such a bonding does not require any material addition and is suitable with an Ultra-High Vacuum (UHV) process. Moreover, since the post-processing steps beyond those described on Fig. 2 will be achieved in an Ultra-High Vacuum chamber, only samples with a size of 1 × 1 cm2 are envisioned. This adds another constraint which concerns the capability for the assembly to be diced into samples, meaning that bonding energy must be high enough to undergo the dicing step without any separation of the wafers.

3.2 Nanoscale Via Achievement by FIB

3.2.1 Backside Deep Cavity Processing

Prior to the fabrication of the connecting path, a cavity as deep as the substrate thickness is etched on the wafer backside. A classical wet anisotropic etching of silicon is carried out with a Tetra-Methyl Ammonium Hydroxide (TMAH) solution. Three square cavity sizes of 1.2, 1.4, and 1.6 mm, respectively, have been chosen (R, S, T notations on Fig. 3). They have been calculated in order to get a bottom surface which edge is about a few hundreds of microns. Regarding the depth of the cavity, etching process duration is about 20 h, meaning that the substrate had to be specifically protected to undergo such an etching duration. When the chip substrate is a SOI substrate, the buried oxide layer is used as an etch stop layer, but care must be taken to avoid any attack of this layer. The SOI characteristics are given as follows: Si 200 nm/Box 400 nm/Si 725 µm. Figure 3 illustrates different cavities obtained on a 725-µm-thick bulk Si substrate (upper images) and a SOI substrate (lower images).

During this step, defects have been observed due to the deep TMAH lateral over-etching. A specific chemical wet cleaning has been developed, and the defects have successfully been removed.

An optical microscope control conducted on the front side SOI substrate after cavity etching is shown on Fig. 4 and demonstrates that the localization marks processed during step 1 can be successfully identified at the center of the membrane.

3.2.2 FIB Tools

Nanovias are fabricated with a FIB tool. The gallium beam enables nanovias etching and filling through the decomposition of a tungsten-based precursor (W(CO)6). The nanovias fabrication process has been developed in two different tools. The first one is a sample-scale FIB where process is developed on a 1-cm2 sample, whereas the second one is a wafer-scale FIB set in a clean room and operating on 200-mm silicon wafers.

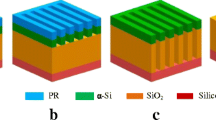

The development of nanovias fabrication processes has first been conducted on Si samples covered with a 400-nm-thick SiO2 layer, mimicking the future SOI substrates used in the final integration flow. The first work has consisted in the control of (i) the nanovia etching stop (at the SiO2/Si interface), (ii) the nanovia geometry, and (iii) the nanovia filling. The second step has consisted in studying the impact of the nanovia fabrication process on the surface reconstruction process and on the final surface quality. The process has finally been transferred at the wafer scale on SOI substrate.

3.2.3 Development of the Nanovia Etching and Filling Processes

In the sample-scale FIB equipment used for the first developments, etching stop has been accurately controlled by monitoring the transmitted current through the Si substrate (accuracy of 5 %), and after further optimization of etching and filling parameters, a well-controlled etching stop at the SiO2/Si interface and a void less filling have been obtained.

When transferring the processes toward a wafer-scale FIB tool, equipped with a detector set farther from the substrate, this method for controlling the etching stop could not be used anymore: nanovias have thus begun to be etched and filled while monitoring the process duration, which requires to adjust etching and filling parameters at the beginning of each experiment to gain accuracy. Etching takes 2 s on average for a 100-nm-diameter nanovia, whereas filling takes between 3 and 8 s.

Regarding nanovia filling, the main difficulty lies in the control of the over-etching as both etching and filling phenomena are co-existing during the filling step. Further optimization on both etching and filling parameters has conducted to voidless nanovias. Nanovias with a geometry of 100 nm in diameter and 400 nm high have been obtained with a good reproducibility. These results are illustrated on Fig. 5.

The use of a gallium beam for the nanovias fabrication raises the question of the management of non-intentionally implanted gallium atoms in the SOI film, and especially as gallium has a low melting point (30 °C), whereas a surface reconstruction process at high temperature (950–1100 °C) ends the integration flow. A study on the impact of the nanovia fabrication process on the surface reconstruction process and on the final surface quality has thus been launched. Three types of nanovias have been fabricated and characterized, in order to simulate the three technological steps at stake: (i) etched nanovias, (ii) etched and thermally treated nanovias (simulation of the surface reconstruction step), and (iii) etched, thermally treated, and filled nanovias (corresponding to the final step of the integration process). Results are illustrated on Fig. 6.

Voids and amorphous areas have been observed at the bottom of some nanovias. On Fig. 6a, an amorphous layer of 50 nm can be observed at the bottom of the nanovia. It can be explained by a high gallium beam current which at least produces a gallium ion implantation in the silicon film and which can result in an amorphous SOI layer. Voids have been observed at the bottom of nanovias after thermal treatment. All the interactions between gallium atoms, cleaning solutions, and thermal treatment have not totally been understood yet and are still under investigation. However, it has been noted that etching stop plays an important role, and it seems that an etching stop in the SiO2 layer could prevent the apparition of void at the SiO2/Si interface after surface reconstruction, as it can be seen on Fig. 6c on the nanovias on the left side of the image. This hypothesis has been the object of a specific study as illustrated on Fig. 7.

Compared to the previous study, an arsenic implantation of the SOI film has been conducted through the 200 nm-diameter nanovias and the dopants have been activated during the thermal treatment at 950 °C. The two configurations, etching stop at the SiO2/Si interface and etching stop in the SiO2 layer, are presented on the TEM picture on Fig. 7. The etching stop and the tungsten filling at the SiO2/Si interface have modified the nanovias geometry (Fig. 7a). The nanovia geometry has been preserved when the etching stop has been achieved in the oxide layer, located several nanometers above the Si/SiO2 interface. The oxide layer at the bottom of the nanovia has protected the silicon surface, and the voids previously observed have not been detected. The connection between the nanopads and the nanovias has been completed with a wet chemical etching containing hydrofluoric acid (Fig. 7b). With this protocol, the amorphous area has been recrystallized during the surface reconstruction process. However, dislocations have been observed in both cases, which leads to the conclusion that these defects have been generated by arsenic implantation at high energy (150 keV).

Figure 8 provides a chemical analysis of the 200 nm-diameter nanovias. It should be noted that the EDX sensitivity is ~0.5 wt% for a given element, which means that the amount of implanted gallium is greater than this detection limit.

Observations on etched nanovias (Fig. 6a) have clearly put forward the presence of a 50 nm-thick amorphous layer at the bottom of etched nanovias. This layer has been identified as a Ga-implanted layer with EDX analysis. Considering now etched and thermally treated nanovias (Fig. 6b), a defective area corresponding to a Ga-implanted region, as evidenced by EDX analysis, is still observed at the bottom of both open and blind nanovias and extends over a thickness of ~200 nm for open nanovias, while it extends over ~50 nm for blind nanovias (as for etched ones). In this late case, the defective area seems to be crystalline, whereas it appears partially amorphous in the case of open nanovias. This is a key point to be taken into account for the future work on the whole integration, as this defective area is in the same order of magnitude as the thickness of the Si film of SOI substrates for open nanovia, whereas it is smaller and becomes crystalline for blind nanovias after thermal treatment. Moreover, unexpected voids have been observed at the extremity of open nanovias, whether they are empty or filled. Such voids have not been observed in the case of blind nanovias and have been specifically observed after thermal treatment (surface reconstruction): no such voids have been observed on etched nanovias. One possible explanation for the presence of such voids could be related to the chemical solutions used in the cleaning step prior to the thermal treatment at 950 °C: assuming the observed voids indeed correspond to a Ga-rich area prior to surface cleaning, this Ga-rich amorphous material may have been etched during surface cleaning. This assumption has however to be further investigated with additional experiments.

Electrical properties of such FIB-fabricated nanovias have furthermore been explored. First, regarding the characterization of the filling material, the electrical resistance of the deposited tungsten has been measured on an appropriate structure and the experimental material resistivity has been found to be two orders of magnitude higher than for the bulk material (experimental value: 2.4 × 10−6 Ω m). This can be explained by the partial dissociation of the W(CO)6 gas under the ion beam, which has been confirmed by the EDX analysis of the nanovia composition (Fig. 9): tungsten has been found as the major element (75 mass%); carbon (10 mass%), oxygen (5 mass%), and Ga traces have also been found. Moreover, there is no composition variation with deposition time leading to a homogeneous material composition over the whole nanovia.

Electrical characterization of the nanovias has been tested through Scanning Spreading Resistance Microscopy (SSRM), which is a probing technique using an AFM in contact mode with a conductive tip. These tests aimed at evidencing conductive areas (W-filled nanovia) in the insulating substrate (SiO2), and at trying to extract nanovias resistance. Nanovias have been successfully evidenced (Fig. 10), but their resistance could not be extracted as it has been found negligible compared to the access resistances. However, a resistance variation over 2 orders of magnitude has been measured between the substrate and the nanovias.

Beside the understanding of the interactions between the etching, filling, and reconstruction processes at the bottom of nanovias, the integration technology has been developed and these processes have been implemented at the wafer scale. Matrices of nanovias have been successfully FIB-etched and filled at the bottom of 480 µm-deep cavities (Fig. 11).

The nanoscale/microscale connection between nanovias and contact pads has been completed through the deposition of tungsten lines along the cavity side, using the same wafer-scale FIB. A continuous electrical path has thus morphologically been demonstrated, on the substrate backside, from nanovias to electrical contact pads (Fig. 12).

3.3 Nanopads Processing

Implanted areas (referred to as nanopads) ensure the electrical continuity between the molecular/atomic circuit on the top surface and the nanovias. Nanopads are fabricated by implanting dopants on the SOI film, from the substrate backside, through FIB-etched nanovias (Fig. 2, step 8). Dopants are activated during surface reconstruction: the thermal budget of this step is however higher than required for dopants activation and diffusion is expected to occur, which implies the nanopads enlargement and possible short-circuit. Two main issues have been addressed:

-

Nanopads spreading during the surface reconstruction process: this point has been investigated by calculation and measurements after dopants diffusion;

-

Impact of doped areas on the surface reconstruction.

3.3.1 Interconnection Resistance Calculation

Dopants diffusion has been simulated, and the expected resistance of the interconnection system has been estimated. Simulation has been performed with the S-Process software (Synopsys). Two doping species have been taken into account: arsenic, which creates a lot of crystal defects when implanted, and phosphorous, which generates a lower defectivity but has a higher diffusivity in silicon than arsenic. The implantation conditions are described in Table 1.

These implantation conditions have been chosen in order to ensure the highest doping level for the nanopads (in order to minimize their electrical resistance), while still enabling the reconstruction of the damaged layer. For this latter point, the implantation energy has been chosen so as to leave a crystal seed of a few tens of nanometers. Monte Carlo simulations have been run and show that the Si film is expected to become amorphous on 180 nm thick after implantation, which lets 20 nm of crystalline silicon to enable the film reconstruction (Fig. 13).

A reconstruction process at 950 °C (rather than the 1100 °C classical process) has been considered in order to reduce dopants diffusion while still enabling surface reconstruction. Several geometries (diameter, spacing) and implantation conditions have been tested, in order to (i) get the smallest gap between nanopads after surface reconstruction while avoiding short-circuit, (ii) get the highest doping level (lowest resistance) while not damaging the surface (i.e., avoiding an amorphous surface).

Process simulations indeed show that the thermal budget used for a surface reconstruction at 950 °C is affordable from nanopads view, adapting nanovias geometry and dopant type. In the case of an As implantation through nanovias of 100 nm in diameter and spaced of 350 nm, the distance between nanopads after diffusion during 12 min at 950 °C is expected to be 125 nm (Fig. 14a), and the doping concentration on the frontside is expected to be about 8 × 1018 at. cm−3 (Fig. 14b). Moreover, the surface treatment process duration does not show a great difference between 6 and 12 min.

The expected resistance of nanovias and nanopads has been calculated, and the results are shown on Fig. 15. It takes into account a nanovia filling with tungsten. A resistance in the range of a few hundreds of ohms is expected. It should be noted that contact resistances have not been considered in this calculation.

Besides, it should be kept in mind that the standard Si substrate resistivity is in the order of 1–50 × 104 Ω µm, namely 25 kΩ–1.25 MΩ for a space of 100 nm between nanovias. This means that the resistance of the Si film might be in the same order of magnitude as the resistance of the molecule/atomic circuit. A way for solving this problem could be to implement this technology on high silicon resistivity substrates (>106 Ω µm).

3.3.2 Nanopad Design

Based on these simulation results, two sets of e-beam lithography masks, namely A and B, have been designed: the mask A aims at evaluating the impact of nanovias fabrication and dopants implantation on the surface properties. It consists in nanopads matrices, with varying diameter, space, and density (Fig. 16a). The mask B intends to evaluate dopants diffusion during surface reconstruction and to measure leakage currents, in order to control the distance between nanopads. It consists in circular patterns of 300 µm in diameter, containing radial lines of either 50 nm or 100 nm wide. This design is more dedicated to SSRM and STM studies (Fig. 16b). Both series of masks are equipped with specific patterns to locate implanted areas.

These two e-beam masks include different nanopads designs, such as (i) the number of implanted pads in the circular patterns, (ii) the doped pads width, and (iii) the distance between the nanopads. Table 2 describes the mask B patterns and geometries (Fig. 16b).

Figure 16 illustrates the above-mentioned designs implemented on a stack composed of: 400 nm thick of e-beam photoresist/400 nm thick of SiO2 layer/silicon substrate. Figure 17a−e respectively correspond to the designs of Fig. 16a, b.

A preliminary surface investigation has been conducted on the sample corresponding of the mask A (Fig. 16a) after photo-resist removal. This experiment has been achieved with an AFM tip (tapping mode). A matrix of 7 × 7 nanopads has been implanted in 12 µm2, thus demonstrating an interconnection density as high as 4 × 106/mm2. Such a structure is shown on Fig. 18.

In the same way, dopants distribution has been investigated after thermal treatment and diffusion at 950 °C with Scanning Capacitance Measurement (SCM). This technique gives a direct correlation between capacitance and dopants concentration. An electrical modulation is applied on the sample, and the capacitance variation correlates to the dopant type. SCM characterization has been conducted on the implanted lines (mask B (Fig. 16b)) with the conditions described in Table 2. Figure 19 illustrates such measurements on a four implanted lines configuration: the yellow part corresponds to the P-doped silicon substrate, while the blue part represents the N-doped areas. This experiment has enabled the measurement of the diffusion length with the distance defined in the mask (before diffusion) as reference. Figure 19a has demonstrated that a short-circuit is experimentally observed with a distance designed at 200 nm. Using a distance of 250 nm between the four electrodes (Fig. 19b), an edge side short-circuit has also been noticed. Regarding the distance of 350 nm between the 4 electrodes (Fig. 19c), no short-circuit between implanted lines has been observed and the distance measured between neighbor’s electrodes after diffusion is 60 nm. This experimental value is in agreement with the distance reported in the simulation after dopants diffusion (125 nm) (Fig. 14a), though it is a bit lower than expected. These first results meet the requirements of STM-based atomic-scale wires and let think that a nano-objet could be deposited and connected between the implanted lines.

Scanning Capacitance Measurement (SCM) pictures with different spacing between four electrodes after surface smoothing at 950 °C. a Short-circuit is observed with a 200 nm distance, b an edge side short-circuit is observed with a 250 nm distance, c no short-circuit is observed with a distance of 350 nm initially designed

3.3.3 Nanopads Impact on Surface Reconstruction and Bonding

A study has been conducted to determine the effect of surface implantation on the bonding quality. The SOI substrate has been implanted according to the nanopads design, and its surface has been reconstructed. Finally, this SOI substrate has been capped with a surface-reconstructed silicon wafer. The fabrication of such a test vehicle has required (i) the fabrication of localization marks intended to ease the finding of nanopads during the characterization phase; (ii) the development of e-beam lithography which has been a challenging part because of the wide range of patterns studied and the thick resist used (400 nm) for implantation; (iii) the implantation of nanopads, using the simulated conditions; and (iv) the surface preparation (cleaning, surface reconstruction at 950 °C), the surface preservation with the hydrophobic bonding of a patterned cap wafer, and dicing. A Scanning Acoustic Microscope (SAM) picture of this test vehicle before dicing is shown on Fig. 20. Bonding defects are put forward (white parts) and appear most of the time on the patterned parts of the substrates corresponding either to implanted areas for the bottom substrate, or to etched bevels for the top one.

A scanning Tunneling Microscopy (STM) characterization has been conducted on the P-implanted samples in order to image the doped surface after reconstruction. The characterizations have been carried out in an Ultra-High Vacuum (UHV) system with a base pressure of 5 × 10−11 mbar. The Low-Temperature STM (LT-STM) measurements have been performed at 4 K with electrochemically etched polycrystalline tungsten tips used as probes. The debonding step has been successfully achieved in the UHV equipment, validating the temporary silicon cap protection concept. Immediately after their debonding, the P-doped samples have been transferred to the cryostat, where they have been cooled down to 4 K. Because of the samples surface preservation with a bonded cap, no additional surface preparation has been applied.

The SiH(001) surface with P-doped Si areas has been investigated, and the result is presented on Fig. 21.

The observation of dimers rows demonstrates that the implanted regions have been correctly rebuilt during the surface reconstruction treatment at 950 °C. However, the surface quality of the P-doped sample is lower than for undoped samples and surface defects have been observed. Surface disorder may indeed have occured during the fabrication of localization marks or during implantation. Although this process requires improvements, it shows that an implanted surface can be properly reconstructed by a surface treatment and it emphasizes the great potential of this technology for the future production of functional electronic devices at the nanoscale.

4 Summary and Conclusion

A new technological field for the packaging of atomic-scale devices on 200 mm SOI substrates has been opened. This technology includes both surface reconstruction and capping, and electrical interconnection developments. The technological developments of the required modules have been described before their integration in a complete process flow. Due to the first requirements on the surface quality, silicon direct bonding has been identified as a suitable technology for the preservation of silicon wafers that have undergone a smoothing surface treatment. This packaging technology is reversible, meaning that it is possible to temporarily protect the device and is strong enough to allow the substrate dicing into chips. The second requirement concerns the interconnections between the atomic-scale circuit and external connection pads. This interconnection is composed of nanopads made of silicon-doped zones in the silicon part of the SOI wafer, connected to nanovias, fabricated in a FIB tool through the oxide layer of the SOI. Prior to the interconnections achievement, a deep cavity has been patterned in the backside of the wafer down to the oxide layer, in order to drill the nanovias. This deep cavity leaves a 600 nm-thick membrane on which the atomic circuit will further be achieved. The interconnection completion, from nanovias to electrical contact pads, has been ensured by tungsten lines deposited by FIB at the bottom of the cavity, and along the cavity sides. The connection between the nanopads (nanometric scale) and the electrical pads on the wafer backside (micrometric scale) has been correctly achieved.

The presented technology relies upon the fabrication of nanovias with a FIB equipment. 100 nm and 200 nm-diameter nanovias have been successfully etched and filled. TEM observations of nanovias have shown an amorphous Ga-implanted area in the silicon part: this layer has been chemically and structurally investigated, and further studies are now needed to achieve the control of this Ga-rich area. Regarding nanovias filling process, it has been achieved with FIB-deposited tungsten which shows a resistivity two orders of magnitude higher than the bulk metal. Electrical measurements performed on a 3 × 3 nanovias matrix have demonstrated that nanovias were clearly insulated from each other’s. The distance between two [nanovias + nanopads] has been simulated and measured by SCM and has demonstrated that the lowest distance separating two 100 nm diameter nanovias was 60 nm. This is in the same order of magnitude as a STM atomic-scale wire. Finally, a substrate equipped with implanted nanopads has been reconstructed and bonded. The observation of this first assembly has not revealed any bonding defect except in the doped or etched parts of the substrate. STM has demonstrated that the reconstruction process at 950 °C was able to rebuilt the amorphous areas created by the deep implantation and has evidenced Si:H dimers on the surface.

Further investigations will be conducted on the surface reconstruction in the presence of dopants, as well as both on the understanding of some fabrication steps of the nanovias, and on the dopants diffusion and characterization. Future work will also address the complete integration and assembly of a SOI and a silicon wafers, and the measurement of the resistance of the whole electrical chain including nanovias and nanopads.

The presented achievements however already demonstrate the great potential of this technology and pave the way for the integration of nano-objects, from nanoelectronics to bioelectronics.

References

Knickerbocker, J.U., Andry, P.S., Dang, B., Horton, R.R., Interrante, M.J., Patel, C.S., Polastre, R.J., Sakuma, K., Sirdeshmukh, R., Sprogis, E.J., Sri-Jayantha, S.M., Stephens, A.M., Topol, A.W., Tsang, C.K., Webb, B.C., Wright, S.L.: Three-dimensional silicon integration. IBM J. Res. Dev. 52(6), 553–569 (2008)

Garrou, P., Koyanagi, M., Ramm, P.: Handbook of 3D Integration. 3D Process Technology, vol. 3. Wiley, New York (2014)

Lau, J.H: Evolution, challenge, and outlook of TSV (through-silicon via) and 3D IC/Si integration. Keynote at IEEE Japan ICEP, 13–15 (2011)

Lau, J.H: Evolution, challenge, and outlook of TSV (through-silicon via) and 3D IC/Si integration. In: Proceedings of 2011 International Symposium on Advanced Packaging Materials (APM), pp. 462–488 (2011)

Gupta, A., Kannan, K., Kim, B., Mohammed, E., Ahn, B.: Development of novel carbon nanotube TSV technology. In: 2010 Electronic Components and Technology Conference, pp. 1699–1702 (2010)

Wang, T., Jeppson, K., Olofsson, N., Campbell, E., Liu, Y.: Through silicon vias filled with planarized carbon nanotube bundles. Nanotechnology 20, 485203 (2009). doi:10.1088/0957-4484/20/48/485203

Wang, T., Jeppson, K., Ye, L., Liu, Y.: Carbon-nanotube through-silicon via interconnects for three-dimensional integration. Small X(XX), 1–5 (2011)

Wang, T., Chen, S., Jiang, D., Fu, Y., Jeppson, K., Ye, L., Liu, L.: Through-silicon vias filled with densified and transferred carbon nanotube forests. IEEE Electron Device Lett. 33(3), 420–422 (2012)

Zhao, W.S., Yin, W.Y., Guo, Y.X.: Electromagnetic compatibility-oriented study on through silicon single-walled carbon nanotube bundle via (TS-SWCNTBV) arrays. IEEE Trans. Electromagn. Compat. 54(1), 149–157 (2012)

Xie, R., Zhang, C., Van der Veen, M.H., Arstila, K., Hantschel, T., Chen, B., Zhong, G., Robertson, J.: Carbon nanotube growth for through silicon via application. Nanotechnology 24,125603 (2013). doi:10.1088/0957-4484/24/12/125603

Morris, J.E. (ed.): Nanopackaging: nanotechnologies and electronics packaging. Springer, Berlin (2008)

Morris, J.E.: Nanotechnology materials for electronics reliability. In: 31st International Spring Seminar on Electronics Technology. ISSE’08, vol. C013, pp. 211–215 (2008)

Schwarzbauer, H., Kuhnert, R.: Novel large area joining technique for improved power device performance. In: Proceedings of Industry Applications Society Annual Meeting, vol. 2, pp. 1348–1351 (1989)

Zhang, Z.Z., Lu, G.Q.: Pressure-assisted low-temperature sintering of silver paste as an alternative die-attach solution to solder reflow. IEEE Trans. Electron. Packag. Manuf. 25(4), 279–283 (2002)

Bai, J.G., Zhang, Z.Z., Calata, J.N., Lu, G.Q.: Low-temperature sintered nanoscale silver as a novel semiconductor device-metallized substrate interconnect material. IEEE Trans. Compon. Packag. Technol. 29(3), 589–593 (2006)

Göbl, C., Faltenbacher, J.: Low temperature sinter technology die attachment for power electronic applications. In: Proceedings of CIPS 2010, 16–18 March 2010, Nuremberg/Germany, Paper 10.1 (2010)

Lei, T.G., Calata, J.N., Lu, G.Q., Chen, X., Luo, S.: Low-temperature sintering of nanoscale silver paste for attaching large-area (>100 mm2) chips. IEEE Trans. Compon. Packag. Technol. 33(1), 98–104 (2010)

Zheng, H., Berry, D., Calata, J.N., Ngo, K.D.T., Luo, S., Lu, G.Q.: Low-pressure joining of large-area devices on copper using nanosilver paste. IEEE Trans. Compon. Packag. Manuf. Technol. 3(6), 915–922 (2013)

Ishida, H., Ogashiwa, T., Yazaki, T., Ikoma, T., Nishimori, T., Kusamori, H., Mizuno, J.: Low-temperature wafer bonding for MEMS hermetic packaging using sub-micron Au particles. Trans. Jpn. Inst. Electron. Packag. 3(1), 62–67 (2010)

Joachim, C. (ed.): Atomic Scale Interconnection Machines. Advances in Atom and Single Molecule Machines. Springer, Berlin (2012)

Lwin, M.H.T., Tun, T.N., Kim, H.H., Kajen, R.S., Chandrasekhar, N., Joachim, C.: Silicon on insulator nanoscale backside interconnects for atomic and molecular scale circuits. J. Vac. Sci. Technol., B 28, 978–984 (2010). doi:10.1116/1.3484248

Le Gac, G., Audoit, G., Thuaire, A., Moriceau, H., Baillin, X.: Nanovias FIB-etching and filling in a micro-nano interposer for molecular electronics. In: Technical Proceedings of the 2012 NSTI Nanotechnology Conference and Expo, NSTI-Nanotech 2012, vol. 2, p. 539 (2012)

Niklaus, F., Stemme, G., Lu, J.-Q., Gutmann, R.J.: Adhesive wafer bonding. J. Appl. Phys. 99, 031101 (2006). doi:10.1063/1.2168512

Hartmann, J.M., Loup, V., Rolland, G., Holliger, P., Laugier, F., Vannuffel, C., Séméria, M.-N.: SiGe growth kinetics and doping in reduced pressure-chemical vapor deposition. J. Cryst. Growth 236, 10–20 (2002)

Kolmer, M., Godlewski, S., Zuzak, R., Wojtaszek, M., Rauer, C., Thuaire, A., Hartmann, J.M., Moriceau, H., Joachim, C., Szymonski, M.: Atomic scale fabrication of dangling bond structures on hydrogen passivated Si(0 0 1) wafers processed and nanopackaged in a clean room environment. Appl. Surf. Sci. 288, 83–89 (2014)

Rauer, C., Rieutord, F., Hartmann, J.M., Charvet, A.-M., Fournel, F., Mariolle, D., Morales, C., Moriceau, H.: Hydrophobic direct bonding of silicon reconstructed surfaces. Microsyst. Technol. 19, 675–679 (2013)

Acknowledgments

This work was supported by the European Community (AtMol project) under grant agreement No 270028.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this paper

Cite this paper

Thuaire, A. et al. (2015). Silicon Technologies for Nanoscale Device Packaging . In: Baillin, X., Joachim, C., Poupon, G. (eds) Nanopackaging: From Nanomaterials to the Atomic Scale. Advances in Atom and Single Molecule Machines. Springer, Cham. https://doi.org/10.1007/978-3-319-21194-7_8

Download citation

DOI: https://doi.org/10.1007/978-3-319-21194-7_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-21193-0

Online ISBN: 978-3-319-21194-7

eBook Packages: Chemistry and Materials ScienceChemistry and Material Science (R0)