Abstract

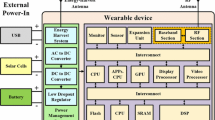

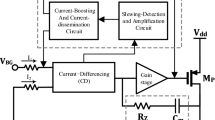

Multiple integrated power regulators with compact size, process extensibility, and low voltage supply are required for an energy efficient system on chip (SoC). Traditional analog low-dropout regulators (ALDOs) may barely achieve all these necessities when digital LDOs (DLDOs) are suitable solutions. The power-speed trade-off, however, limits the naturally slow transient response of the typical DLDO with synchronous control DLDOs, and fully turned-on power switches may lead to power supply ripples, resulting in poor power supply rejection (PSR). In this paper, a comparative study between ALDOs and DLDOs is presented. We first generally weigh the advantages and disadvantages of ALDOs and DLDOs. The latest DLDO strategies for quick transient response and PSR improvement are briefly discussed next. Finally, we discuss current design trends and potential DLO developments.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Meinerzhagen, P.A., et al.: An Energy-Efficient Graphics Processor in 14-nm Tri-Gate CMOS Featuring Integrated Voltage Regulators for Fine-Grain DVFS. Retentive Sleep, and VMIN Optimization, in IEEE Journal of Solid-State Circuits 54(1), 144–157 (2019). https://doi.org/10.1109/JSSC.2018.2875097

Nasir, S.B., Gangopadhyay, S., Raychowdhury, A., “5.6 A 0.13μm fully digital low-dropout regulator with adaptive control and reduced dynamic stability for ultrawide dynamic range,”,: IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers. San Francisco, CA, USA 2015, 1–3 (2015). https://doi.org/10.1109/ISSCC.2015.7062944

Chong, Chan, P.K.: A 0.9-/spl mu/A quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS, In: IEEE Transactions on Circuits and Systems I: regular papers 60(4), pp. 1072–1081 (2013)https://doi.org/10.1109/TCSI.2012.2215392

Lu, Y., Wang, Y., Pan, Q., Ki, W.-H., Yue, C.P.: A Fully Integrated Low-Dropout Regulator with Full-Spectrum Power Supply Rejection. IEEE Trans. Circuits Syst. I Regul. Pap. 62(3), 707–716 (2015). https://doi.org/10.1109/TCSI.2014.2380644

Huang, M., Feng, H., Lu, Y.: A Fully Integrated FVF-Based Low-Dropout Regulator with Wide Load Capacitance and Current Ranges. IEEE Trans. Power Electron. 34(12), 11880–11888 (2019). https://doi.org/10.1109/TPEL.2019.2904622

Cai, G., Zhan, C., Lu, Y., Fast-Transient-Response Fully Integrated Digital, A., LDO with Adaptive Current Step Size Control,: IEEE International Symposium on Circuits and Systems (ISCAS). Sapporo, Japan 2019, 1–4 (2019). https://doi.org/10.1109/ISCAS.2019.8702758

Park, C. -J., Onabajo, M., Silva-Martinez, J.: External capacitor-less low Drop-out regulator With 25 DB Superior power supply rejection in the 0.4–4 MHz Range, In: IEEE J. Solid-State Circuits. 49(2), pp. 486–501 (2014) https://doi.org/10.1109/JSSC.2013.2289897

Lu, Y., Martins, R.P., Seng-Pan, U., et al.: A 312 ps response-time LDO with enhanced super source follower in 28 nm CMOS. Electron Lett 52, 1368 (2016)

V. Gupta, G. A. Rincon-Mora and P. Raha, Analysis and design of monolithic, high PSR, linear regulators for SoC applications, IEEE International SOC Conference: Proceedings. Santa Clara, CA, USA 2004, 311–315 (2004)https://doi.org/10.1109/SOCC.2004.1362447

de Groot, A.C., Toonstra, J.: 10. In: Casuïstiek in de dermatologie deel Bohn Stafleu van Loghum, Houten 2, pp. 33–36 (2010)https://doi.org/10.1007/978-90-313-8458-7_10

Huang, M., Lu, Y., Sin,S.-W., U, S. -P., Martins, R.P., Ki, W.-H.: Limit Cycle Oscillation Reduction for Digital Low Dropout Regulators, in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 63, no. 9, pp. 903–907, Sept. 2016, doi: https://doi.org/10.1109/TCSII.2016.2534778

Nasir, S.B., Raychowdhury, A., On limit cycle oscillations in discrete-time digital linear regulators,: IEEE Applied Power Electronics Conference and Exposition (APEC). Charlotte, NC, USA 2015, 371–376 (2015). https://doi.org/10.1109/APEC.2015.7104377

Huang, M., Lu, Y., Sin, S.-W., Seng-Pan, U., Martins, R.P.: A Fully Integrated Digital LDO With Coarse–Fine-Tuning and Burst-Mode Operation. IEEE Trans. Circuits Syst. II Express Briefs 63(7), 683–687 (2016). https://doi.org/10.1109/TCSII.2016.2530094

Salem, L.G., Warchall, J., Mercier, P.P.: A Successive Approximation Recursive Digital Low-Dropout Voltage Regulator with PD Compensation and Sub-LSB Duty Control. IEEE J. Solid-State Circuits 53(1), 35–49 (2018). https://doi.org/10.1109/JSSC.2017.2766215

Huang, M., Lu, Y,, Seng-Pan, U., et al.: An output-capacitor-free ana-log-assisted digital low-dropout regulator with tri-loop control. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), 342 (2017)

M. Huang, Y. Lu, S. -P. U and R. P. Martins, An Analog-Assisted Tri-Loop Digital Low-Dropout Regulator, in IEEE Journal of Solid-State Circuits, vol. 53, no. 1, pp. 20–34, Jan. 2018, doi: https://doi.org/10.1109/JSSC.2017.2751512

Huang, M., Lu, Y., Lu, X.: Partial analog-assisted digital low dropout regulator with transient body-drive and 2.5 × FOM improvement. Electron Lett. 54, 282 (2018)

Ma, X., Lu, Y., Martins, R.P., Li, Q., A 0.4 V 430nA quiescent current NMOS digital LDO with NAND-based analog-assisted loop in 28 nm CMOS,: IEEE International Solid - State Circuits Conference - (ISSCC). San Francisco, CA, USA 2018, 306–308 (2018). https://doi.org/10.1109/ISSCC.2018.8310306

Akram, M.A., Hong, W., Hwang, I.C.: Fast transient fully standard-cell-based all digital low-dropout regulator with 99.97% current efficiency. IEEE Trans Power Electron. 33, 8011 (2018)

Sun, X., Boora, A., Zhang, W., Pamula, V.R., Sathe, V., 14.5 A 0.6-to-1.1 V Computationally Regulated Digital LDO with 2.79-Cycle Mean Settling Time and Autonomous Runtime Gain Tracking in 65 nm CMOS,: IEEE International Solid- State Circuits Conference - (ISSCC). San Francisco, CA, USA 2019, 230–232 (2019). https://doi.org/10.1109/ISSCC.2019.8662298

Lee, Y.-J., et al.: A 200-mA Digital Low Drop-Out Regulator with Coarse-Fine Dual Loop in Mobile Application Processor. IEEE J. Solid-State Circuits 52(1), 64–76 (2017). https://doi.org/10.1109/JSSC.2016.2614308

Kim, D., Seok, M., 8.2 Fully integrated low-drop-out regulator based on event-driven PI control,: IEEE International Solid-State Circuits Conference (ISSCC). San Francisco, CA, USA 2016, 148–149 (2016). https://doi.org/10.1109/ISSCC.2016.7417950

Gangopadhyay, S., Somasekhar, D., Tschanz, J.W., Raychowdhury, A.: A 32 nm Embedded, Fully Digital, Phase-Locked Low Dropout Regulator for Fine Grained Power Management in Digital Circuits. IEEE J. Solid-State Circuits 49(11), 2684–2693 (2014). https://doi.org/10.1109/JSSC.2014.2353798

Kundu, S., Liu, M., Wen, S.-J., Wong, R., Kim, C.H.: A Fully Integrated Digital LDO With Built-In Adaptive Sampling and Active Voltage Positioning Using a Beat-Frequency Quantizer. IEEE J. Solid-State Circuits 54(1), 109–120 (2019). https://doi.org/10.1109/JSSC.2018.2870558

Lee, Y.-H., et al.: A Low Quiescent Current Asynchronous Digital-LDO With PLL-Modulated Fast-DVS Power Management in 40 nm SoC for MIPS Performance Improvement. IEEE J. Solid-State Circuits 48(4), 1018–1030 (2013). https://doi.org/10.1109/JSSC.2013.2237991

Yang, F., Mok, P.K.T.: A Nanosecond-Transient Fine-Grained Digital LDO With Multi-Step Switching Scheme and Asynchronous Adaptive Pipeline Control. IEEE J. Solid-State Circuits 52(9), 2463–2474 (2017). https://doi.org/10.1109/JSSC.2017.2709311

Lu, Y., Huang, M., Martins, R.P.: PID Control Considerations for Analog-Digital Hybrid Low-Dropout Regulators (Invited Paper), In: 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi'an, China, pp. 1–3, (2019)https://doi.org/10.1109/EDSSC.2019.8754302

Kim, S.T., 8.6 Enabling wide autonomous DVFS in a 22 nm graphics execution core using a digitally controlled hybrid LDO, switched-capacitor VR with fast droop mitigation, et al.: IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers. San Francisco, CA, USA 2015, 1–3 (2015). https://doi.org/10.1109/ISSCC.2015.7062972

Zhang, Y., Song, H., Zhou, R., Rhee, W., Shim, I., Wang, Z.: A Capacitor-Less Ripple-Less Hybrid LDO With Exponential Ratio Array and 4000x Load Current Range. IEEE Trans. Circuits Syst. II Express Briefs 66(1), 36–40 (2019). https://doi.org/10.1109/TCSII.2018.2834899

Wang, X., Mercier, P.P.: A Dynamically High-Impedance Charge-Pump-Based LDO With Digital-LDO-Like Properties Achieving a Sub4-fs FoM. IEEE J. Solid-State Circuits 55(3), 719–730 (2020). https://doi.org/10.1109/JSSC.2019.2960004

Nasir, S.B., Sen, S., Raychowdhury, A.: Switched-Mode-Control Based Hybrid LDO for Fine-Grain Power Management of Digital Load Circuits. IEEE J. Solid-State Circuits 53(2), 569–581 (2018). https://doi.org/10.1109/JSSC.2017.2767183

Liu, X., 14.7 A Modular Hybrid LDO with Fast Load-Transient Response and Programmable PSRR in 14 nm CMOS Featuring Dynamic Clamp Tuning and Time-Constant Compensation, et al.: IEEE International Solid- State Circuits Conference - (ISSCC). San Francisco, CA, USA 2019, 234–236 (2019). https://doi.org/10.1109/ISSCC.2019.8662343

Huang, M., Lu, Y., Digital, A.-P.-I.-L., LDO with Fast Response, Improved PSR and Zero Minimum Load Current,: IEEE Custom Integrated Circuits Conference (CICC). Austin, TX, USA 2019, 1–4 (2019). https://doi.org/10.1109/CICC.2019.8780307

Huang, M., Lu, Y., Martins, R.P.: An Analog-Proportional Digital-Integral Multiloop Digital LDO With PSR Improvement and LCO Reduction. IEEE J. Solid-State Circuits 55(6), 1637–1650 (2020). https://doi.org/10.1109/JSSC.2020.2967540

Bang, S., 25.1 A Fully Synthesizable Distributed and Scalable All-Digital LDO in 10 nm CMOS, et al.: IEEE International Solid- State Circuits Conference - (ISSCC). San Francisco, CA, USA 2020, 380–382 (2020). https://doi.org/10.1109/ISSCC19947.2020.9063040

Y. Li, X. Zhang, Z. Zhang and Y. Lian, A 0.45-to-1.2-V Fully Digital Low-Dropout Voltage Regulator with Fast-Transient Controller for Near/Subthreshold Circuits, in IEEE Transactions on Power Electronics, vol. 31, no. 9, pp. 6341–6350, Sept. 2016, doi: https://doi.org/10.1109/TPEL.2015.2506605

Oh, J., Park, J.-E., Hwang, Y.-H., Jeong, D.-K.: 25.2 A 480mA Output-Capacitor-Free Synthesizable Digital LDO Using CMP- Triggered Oscillator and Droop Detector with 99.99% Current Efficiency, 1.3ns Response Time, and 9.8A/mm2 Current Density, 2020 IEEE International Solid- State Circuits Conference - (ISSCC), San Francisco, CA, USA, pp. 382-384 (2020)https://doi.org/10.1109/ISSCC19947.2020.9063018

Singh, A., et al.: A Digital Low-Dropout Regulator with Autotuned PID Compensator and Dynamic Gain Control for Improved Transient Performance Under Process Variations and Aging. IEEE Trans. Power Electron. 35(3), 3242–3253 (2020). https://doi.org/10.1109/TPEL.2019.2930490

Ahmed, Z.K., Variation-Adaptive Integrated Computational Digital, A., LDO in 22 nm CMOS with Fast Transient Response, et al.: Symposium on VLSI Circuits. Kyoto, Japan 2019, C124–C125 (2019). https://doi.org/10.23919/VLSIC.2019.8778070

Lu, Y., Yang, F., Chen, F., Mok, P.K.T., A 500mA analog-assisted digital-LDO-based on-chip distributed power delivery grid with cooperative regulation and IR-drop reduction in 65 nm CMOS,: IEEE International Solid - State Circuits Conference - (ISSCC). San Francisco, CA, USA 2018, 310–312 (2018). https://doi.org/10.1109/ISSCC.2018.8310308

Hazucha, P., Karnik, T., Bloechel, B.A., Parsons, C., Finan, D., Borkar, S.: Area-efficient linear regulator with ultrafast load regulation. IEEE J. Solid-State Circuits 40(4), 933–940 (2005). https://doi.org/10.1109/JSSC.2004.842831

Duong, Q.-H., et al.: Multiple-Loop Design Technique for High-Performance Low-Dropout Regulator. In: IEEE J. Solid-State Circuits 52(10), 2533–2549 (2017). https://doi.org/10.1109/JSSC.2017.2717922

Khadiri, K.E., Qjidaa, H.: A low noise, high PSR low-dropout regulator for low-cost portable electronics, 2013 ACS International Conference on Computer Systems and Applications (AICCSA), Ifrane, Morocco, pp. 1–5, (2013) https://doi.org/10.1109/AICCSA.2013.6616415

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

El Mouzouade, S., El Khadiri, K., Qjidaa, H., Jamil, M.O., Tahiri, A. (2023). Digital vs Analog Low Dropout Regulators a Comparative Study. In: Motahhir, S., Bossoufi, B. (eds) Digital Technologies and Applications. ICDTA 2023. Lecture Notes in Networks and Systems, vol 669. Springer, Cham. https://doi.org/10.1007/978-3-031-29860-8_77

Download citation

DOI: https://doi.org/10.1007/978-3-031-29860-8_77

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-29859-2

Online ISBN: 978-3-031-29860-8

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)