Abstract

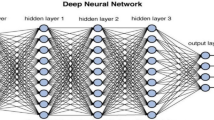

A breakthrough in Machine Learning (ML) based technologies has been seen during last years. To overcome energy, latency and security issues, new concepts are developed to bring the ML codes, namely the Artificial Neural Network (ANN), closer to the systems (Edge-Computing devices, AI-dedicated hardware, smart embedded systems, and derivatives). In this paper, we present a modular implementation approach of the Feed-Forward ANN using LabView VIs and compiled on a Field Programmable Gate Array (FPGA) board embedded in the NI Elvis III station, and we explore the number of resources required to run each part of the ANN modules (Look-Up-Table (LUT) slices, RAM blocks, Register slices, and DSP slices). The modular programming of the ANN allows getting detailed percentages of the resource allocation and helps identifying the most resource-hungry module of the ANN. The experimental results of the ANN implementation on the FPGA show that the LUT represents the highest percentage of the FPGA resource used by the different ANN modules (Input generation, desired output, Loss Function, Update Function, Feed-Forward). The second most used resource is the Register Slices, followed by the DSPs then the block of RAMs. The experiment also shows that the Feed-Forward module of the ANN is the most resource-hungry due to the computation and normalization of the ANN mathematical functions.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Xiaoxuan, W., Feiyu, Z., Ping, L., Yongming, C.: Evaluating computing performance of deep neural network models with different backbones on IoT-based edge and cloud platforms. Internet of Things 20(100609), 2542–6605 (2022)

Marketsandmarkets Research Private Ltd., Edge AI Hardware Market Highlights, Marketsandmarkets Research Private Ltd., US (2022)

Ferreira, P., Ribeiro, P., Antunes, A., Dias, F.M.: A high bit resolution FPGA implementation of a FNN with a new algorithm for the activation function. Neurocomputing. 71(1–3), pp. 71–77 (2007)

Gomperts, A., Ukil, A., Zurfluh, F.: Development and Implementation of Parameterized FPGA Based General Purpose Neural Networks for Online Applications. In: IEEE Trans. Industr. Inf. 7(1), 78–89 (2011)

Baptista, D., Rodrigues, S., Freitas, F., Vasconcelos, R., Morgado-Dias, F.: A survey of software and hardware use in Artificial Neural Networks, Neural Comput. Appl. 23 (3–4), pp. 591–599, 2013

Baptista, D., Rodrigues, S., Freitas, F., Vasconcelos, R., Morgado-Dias, F.: Automatic general-purpose neural hardware generator. Neural Comput Applic, Neural Comput. Appl. 28, pp. 25–36, 2017

Baptista, D., Rodrigues, S., Freitas, F., Vasconcelos, R., Morgado-Dias, F.: A software tool for automatic generation of neural hardware. Int. Arab. J. Inf. Technol., 11(3) (2013)

Rocha, L.M.G.: Energy-Efficient recurrent neural network hardware architecture for heart rate estimation based on photoplethysmography, Federal University of Rio Grande do Sul, (2020)

Taher, H., Grasso, V., Tawfik, S., Gumbs, A.: Artificial Intelligence Surgery The challenges of deep learning in artificial intelligence and autonomous actions in surgery: a literature review, Artif. Intell. Surg. 2, pp. 144–58 (2022) https://doi.org/10.20517/ais.2022.11

Nesrine, W., Hichem, K., Nédra, M.: Improved Arabic Alphabet Characters Classification Using Convolutional Neural Networks (CNN) Comput. Intell. Neurosci.(2022)

What is LabVIEW?, NATIONAL INSTRUMENTS, Nov 2022 https://www.ni.com/en-lb/shop/labview.html

NI ELVIS III, NATIONAL INSTRUMENTS, Nov 2022https://www.ni.com/en-lb/support/model.ni-elvis-iii.html

Atibi, M., Boussaa, M., Issam, A., Bennis, A., Tabaa, M.: Hardware Implementation of Roadway Classification System in FPGA Platform. in Smart Applications and Data Analysis. SADASC , 2020

Bossoufi, B., Lagrioui, A.: High Performance Predictive Control for Permanent Magnet Synchronous Machine Drive: FPGA-Based Implementation. In: Motahhir, S., Bossoufi, B. (eds.) ICDTA 2021. LNNS, vol. 211, pp. 387–398. Springer, Cham (2021). https://doi.org/10.1007/978-3-030-73882-2_36

Gomes, A.T.O., Saadi, M., Silva, B., Rosa, R., Rodriguez, D.Z.: An FPGA-Based Performance Evaluation of Artificial Neural Network Architecture Algorithm for IoT, Wireless Pers. Commun. 127, pp. 11–12 (2021) https://doi.org/10.1007/s11277-021-08566-1

Maddiboyina, H.V., Sankar Ponnapalli, V.A., Naresh Kumar, A.: A Study on the Implementation of Secure VANETs Using FPGA, Recent Innovations in Computing no. Springer, Singapore, pp. 179–187, 2022

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Baccar, N., Hammi, S., Kallel, H. (2023). Resource Allocation of a Modular ANN Implementation Using LabView and FPGA Board. In: Motahhir, S., Bossoufi, B. (eds) Digital Technologies and Applications. ICDTA 2023. Lecture Notes in Networks and Systems, vol 669. Springer, Cham. https://doi.org/10.1007/978-3-031-29860-8_76

Download citation

DOI: https://doi.org/10.1007/978-3-031-29860-8_76

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-29859-2

Online ISBN: 978-3-031-29860-8

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)